# **Data Sheet For SD Memory Slave Controller**

## **FPGA Implementation**

iW-EMDMC-DS-01 R 1.0 31<sup>st</sup> May, 2011

## Table of Contents

| 1. | GENERAL DESCRIPTION                        | 5  |

|----|--------------------------------------------|----|

| 2. | FEATURES                                   | 5  |

| 3. | BLOCK DIAGRAM                              | 7  |

| 4. | PINNING INFORMATION                        | 7  |

| 5. | FUNCTIONAL DESCRIPTION                     | 11 |

| 6. | SD MEMORY STANDARD SLAVE REGISTER OVERVIEW | 12 |

| 7. | TIMING WAVEFORMS                           | 13 |

| 8. | RESOURCE UTILIZATION                       | 15 |

# **List Of Figures**

| Figure 1: FPGA Block Diagram                                     | 7 |

|------------------------------------------------------------------|---|

| Figure 2: Command to Response Waveform                           |   |

| Figure 3: Single Block Write 1-bit Mode Waveform                 |   |

| Figure 4: Single Block Write 4-bit Mode Waveform                 |   |

| Figure 5: Single Block Write 1-bit Mode Waveform(User Interface) |   |

| Figure 6: Single Block Read Waveform                             |   |

# List Of Tables

| Table 1: System Interface IO Signal Description                          | 7  |

|--------------------------------------------------------------------------|----|

| Table 2: SD Memory Interface IO Signal Description                       | 8  |

| Table 3: User Application Data Path Interface IO Signal Description      | 8  |

| Table 4: User Application Command Path Interface IO Signal Description 1 | 10 |

| Table 5: Register List                                                   | 12 |

| Table 6: Device Utilization Summary for Actel ProASIC3E1                 |    |

## **1. General Description**

The SD Memory Slave controller is designed to resides within SD Memory and SDIO card. It serve as a Interface between SD bus and user application logic that provides actual function to the card. The SD memory Slave Controller is targeted into Actel Smart fusion FPGA. This slave controller provides simple and general-purpose 8-bit interface to user application. This Supports 1-bit and 4-bit SD Mode and feature like CRC generation and checking for command, response and data transfer.

The SD Memory slave controller receives commands from the host through the SD Memory interface. The standard SD register set is also implemented within the slave controller and process by the core. This support all mandatory SD Command Classes. The user interface block interfaces SD slave controller and user application through a 8-bit general purpose user interface for data transfer. The user interface block has a separate FIFO for read and write data buffering. A WDT is implemented in the user logic to support timeout logic for user interface application transaction.

## 2. Features

Following are the main features of the SD Memory Slave Controller:

- Compliant with SD Physical Specification Version 2.00

- Supports 1-bit and 4-bit SD Mode

- Supports Standard and High Capacity operations

- Supports Default and High Speed Modes of operation

- Supports all mandatory slave registers set

- CID Register fields are configurable through header file

- Supports only Standard command set

- Supports all mandatory SD Command Classes

- Class 0(Basic Commands)

- o CMD0

- o CMD2

- o CMD3

- o CMD6

- o CMD7

- o CMD8

- o CMD9

- o CMD10

- CMD12

- CMD13

- o CMD15

- Class 2(Block Read Commands)

- o CMD16

- o CMD17

- o CMD18

- Class 4(Block Write Commands)

- o CMD16

- o CMD24

- o CMD25

- Class 5(Erase Commands)

- o CMD32

- o CMD33

- o CMD38

- Class 8(Application Specific)

- CMD55

- o ACMD6

- o ACMD13

- ACMD22

- ACMD23

- ACMD41

- ACMD42

- ACMD51

- Class 10(Switch Commands)

- o CMD6

- CRC7 checking/generation for Command/Response

- CRC16 checking/generation for Data transfer

- Support Maximum block length of 512 bytes

- Supports Single and Multiple block read and write data transfer

- Supports Partial and Misalign Block length option

- SD Memory only implementation

- IP provides simple and general-purpose 8-bit interface to user application

- Combo card features are not supported

- SPI Mode is not supported

- Card Lock/Unlock Operation is not supported.

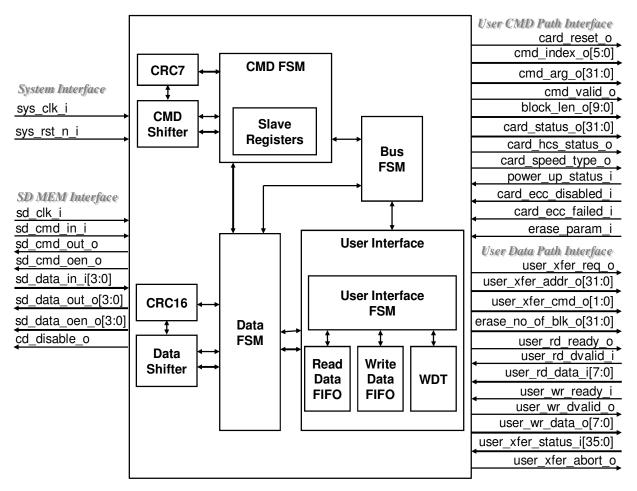

# 3. Block Diagram

## 4. Pinning Information

Table 1: System Interface IO Signal Description

| Signal      | Туре | Width | Description                                           |

|-------------|------|-------|-------------------------------------------------------|

| sys_rst_n_i | Ι    | 1     | System Reset.<br>Active Low Asynchronous reset input. |

| Signal    | Туре | Width | Description                                                                        |

|-----------|------|-------|------------------------------------------------------------------------------------|

| sys_clk_i | Ι    | 1     | System Clock.<br>Clock input to the FPGA This clock is used for<br>the user logic. |

#### Table 2: SD Memory Interface IO Signal Description

| Signal        | Туре | Width | Description                                                                                                                             |  |

|---------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| sd_clk_i      | Ι    | 1     | SDIO Bus Clock input.                                                                                                                   |  |

| sd_cmd_in_i   | Ι    | 1     | SDIO Command input                                                                                                                      |  |

| sd_cmd_out_o  | 0    | 1     | SDIO Response output                                                                                                                    |  |

| sd_cmd_oen_o  | 0    | 1     | SDIO Output enable                                                                                                                      |  |

| sd_data_in_i  | Ι    | 4     | SDIO Data input                                                                                                                         |  |

| sd_data_out_o | 0    | 4     | SDIO Data output                                                                                                                        |  |

| sd_data_oen_o | 0    | 4     | SDIO Data enable output                                                                                                                 |  |

| cd_disable_o  | 0    | 1     | Connect/ Disconnect the 10K-90K ohm pull-up<br>resistor The pull-up may be used for card<br>detection.<br>0 → Connect<br>1 → Disconnect |  |

#### Table 3: User Application Data Path Interface IO Signal Description

| Signal          | Туре | Width | Description                                                                                                |

|-----------------|------|-------|------------------------------------------------------------------------------------------------------------|

| user_xfer_req_0 | 0    | 1     | User Application Request signal.<br>For every new command user request is asserted<br>for one clock cycle. |

### Data Sheet for SD Memory Slave Controller FPGA Implementation

### R 1.0

| Signal                  | Туре | Width    | Description                                                                                                                                                 |

|-------------------------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Type | ,, iutii | -                                                                                                                                                           |

| user_xfer_addr_o[31:0]  | О    | 32       | User Application Address Output<br>Standard Capacity Card -> It is in byte unit.<br>High Capacity Card -> It is block (512 Byte) unit                       |

| user_xfer_cmd_o[1:0]    | О    | 2        | User Application Command Output<br>00 -> Erase Command<br>01 -> Erase and then Write Command<br>10 -> Write Command<br>11 -> Read Command                   |

| erase_no_of_blk_o[31:0] | Ο    | 32       | Indicates no. of Block to be erased.<br>This field is valid when user_xfer_cmd_o is "00"<br>or "01"                                                         |

| user_rd_ready_o         | О    | 1        | User Application read ready signal.<br>This signal indicates SD slave controller is ready<br>to receive the data.                                           |

| user_rd_dvalid_i        | Ι    | 1        | User Application read data valid signal.<br>When valid data is available in user_rd_data_i<br>bus, this is signal will be high.                             |

| user_rd_data_i[7:0]     | Ι    | 8        | User Application read data bus input<br>SD Slave controller latch the user read data when<br>user_rd_ready_o signal and user_rd_dvalid_i<br>signal is high. |

| user_wr_ready_i         | Ι    | 1        | User Application Write ready input signal<br>This signal indicates the user application is ready<br>to receive the data.                                    |

| user_wr_dvalid_o        | О    | 1        | User Application Write data valid output signal.<br>SD Slave controller drive high when valid write<br>data available on user_wr_data_o bus.                |

| user_wr_data_o[7:0]     | 0    | 8        | User Application Write data output bus.                                                                                                                     |

| Signal                    | Туре | Width | Description                                                                                                                                                                        |

|---------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| user_txfer_status_i[35:0] | I    | 36    | User transfer status input<br>[35] -> Erase successful<br>[34] -> Erase failed<br>[33] -> Write successful<br>[32] -> Write failed<br>[31:0] -> No. of blocks written successfully |

| user_xfer_abort_o         | 0    | 1     | User transfer abort signal.<br>When user application is responding for long<br>time then slave controller will abort the current<br>transfer cycle.                                |

### Table 4: User Application Command Path Interface IO Signal Description

| Signal              | Туре | Width | Description                                                                                                                                                                       |  |

|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| card_reset_o        | 0    | 1     | Active high card reset output signal                                                                                                                                              |  |

| cmd_index_o[5:0]    | 0    | 6     | Received host command output                                                                                                                                                      |  |

| cmd_arg_o[31:0]     | 0    | 32    | Received host command argument output                                                                                                                                             |  |

| cmd_valid_o         | 0    | 1     | Received host command valid output                                                                                                                                                |  |

| block_len_o[9:0]    | 0    | 10    | SD Block length output                                                                                                                                                            |  |

| card_status_o[31:0] | 0    | 32    | SD Slave card status register output                                                                                                                                              |  |

| card_hcs_status_o   | 0    | 1     | <ul> <li>SD Slave card capacity type output</li> <li>0 – SD Slave configured as standard Capacity</li> <li>Card</li> <li>1 - SD Slave configured as high Capacity Card</li> </ul> |  |

| card_speed_type_o   | 0    | 1     | SD Slave card speed type output<br>0 – SD Slave operating in default speed (25MHz)<br>1 – SD Slave operating in high speed mode (50<br>MHz)                                       |  |

| Signal              | Туре | Width | Description                                         |

|---------------------|------|-------|-----------------------------------------------------|

| power_up_status_i   | Ι    | 1     | Power Up Status input                               |

| card_ecc_disabled_i | Ι    | 1     | Card ECC Disable Status input                       |

| card_ecc_failed_i   | Ι    | 1     | Card ECC Failed Status input                        |

| erase_param_i       | Ι    | 1     | Invalid Selection of write blocks for erase occured |

## **5. Functional Description**

The SD Memory Slave Controller is targeted into Actel Smart Fusion FPGA. The description of each blocks are listed below:

- **Command FSM:** The command path state machine controls the reception of Command and transmission of Response. Depending on the mode of operation, it generates appropriate control signals to the shifter and CRC7 block. It also parses the command received and generates suitable response output according to rules described in Specification, based on inputs from CRC7 block and Slave FSM. For every command, errors will be updated in the response flags of corresponding response.

- **Command Shifter:** The Command Transmitter and Response Receiver block has a 128bit "Shift Register", it is used to receive and shift in the Command bits and transmit out the Response bits towards the Host. After it receives the complete command, it latches the value and passes it to the Command FSM for further processing. The incoming serial Command data is also passed to the CRC7 block to check for CRC. The serial Response data out is also passed to the CRC7 block to calculate CRC value. It appends the 7-bit CRC during response transmission.

- **CRC7:** The CRC7 module generates CRC Checksum for the 48-bit response generated by the SD Response Block. It calculates the CRC checksum for the start bit, transmission bit, command index and command argument (or card status). The CRC value computed crc7\_calc\_o is then shifted out after the response data when the crc7\_shift\_i is asserted by the SD Command FSM.

- Slave FSM: The SD slave Bus State Machine controls the overall operation of the SD memory controller operation. It defines the Bus States and their relations to SD Commands. The accepted commands indicated along with the individual states apply to SD Mode of operation.

- **Data FSM:** The Data FSM block controls the process of data being transmitted from the SD card to host during read operations or data being received by the SD card from the host during write operations.

- **Data Shifter:** The data Transmitter and Response Receiver block has a 8-bit "Shift Register". For data path, since SD operates in 4-bit mode or 1-bit mode, during transmission the data stored in the shifter is shifted out on bit by bit or 4-bit by 4-bit on data line/s. Similarly during reception, the data comes to the shifter bit by bit or 4-bit by 4-bit is shifted in and accumulate on it.

- **CRC16:** During data transmission, the CRC generator calculates CRC checksum for all data bits in a single block. When the Data FSM Module completes transmission of serial data it enables serial shifting of CRC16 value by asserting crc16\_shift\_i input. The same module acts as a CRC checker during data reception. CRC is calculated over the received data and CRC to result in a value of zero. For data in 4-bit mode, CRC16 is calculated separately for each data line.

- User Interface: The user interface block interfaces SD slave controller and user application through a 8-bit general purpose user interface for data transfer. The user application has a separate FIFO for read and write data buffering. A WDT is implemented in the user logic to implement system timeout logic for user interface transaction.

## 6. SD Memory Standard Slave Register Overview

The Register list of the SD Memory Slave Controller is as shown below.

| Table 5: | Register | List |

|----------|----------|------|

|----------|----------|------|

| Sl.<br>No | Registers                                              | Width | Read/<br>Write | Address Offset |

|-----------|--------------------------------------------------------|-------|----------------|----------------|

| 1.        | Card Identification Register(CID)                      | 128   | R              | -              |

| 2.        | Relative Card Address Register(RCA)                    | 16    | R              | -              |

| 3.        | Card Specific Data Register (CSD) for storage capacity | 128   | R              | -              |

| 4.        | Card Specific Data Register (CSD) for<br>High capacity | 128   | R              | -              |

| 5.        | SD Card Configuration Register (SCR)                   | 64    | R              | -              |

| 6.        | Operation Condition Register (OCR)                     | 32    | R              | -              |

| 7.        | SD Status Register (SSR)                               | 512   | R              | -              |

| 8.        | Card Status Register (CSR)                             | 32    | R              | -              |

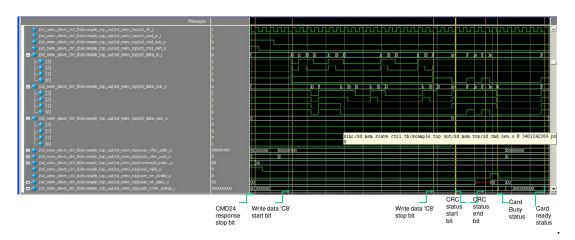

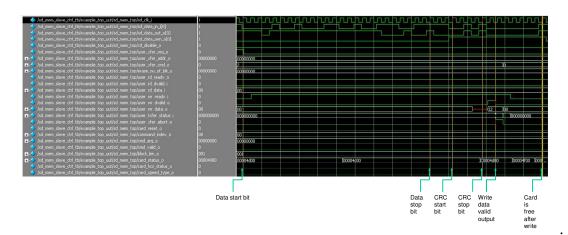

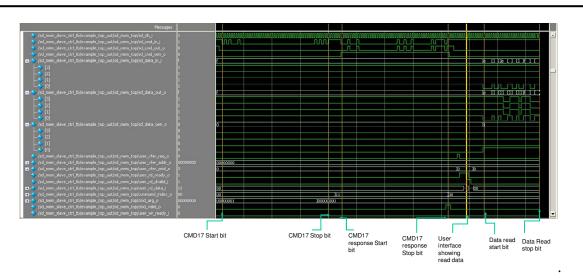

# 7. Timing Waveforms

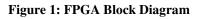

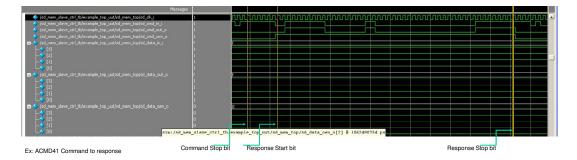

Below waveforms shows the timing diagram of SD Memory Slave Controller.

Figure 2: Command to Response Waveform

Figure 3: Single Block Write 1-bit Mode Waveform

Figure 4: Single Block Write 4-bit Mode Waveform

Figure 5: Single Block Write 1-bit Mode Waveform(User Interface)

Figure 6: Single Block Read Waveform

## 8. Resource Utilization

The table below shows the utilization summary from the implementation of SD Memory Slave Controller for FPGA devices.

| Logic Utilization         | Used |

|---------------------------|------|

| Number of Core SEQ        | 2358 |

| Number of Core COMB       | 3642 |

| Number of RAM /FIFO Block | 4    |

| Number of IOs             | 220  |

Table 6: Device Utilization Summary for Actel ProASIC3E

| Logic Utilization         | Used |

|---------------------------|------|

| Number of Slice Registers | 1512 |

| Number of Slice LUTs      | 1405 |

| Number of RAMB8BWERs      | 2    |

| Number of IOs             | 220  |

#### Table 8: Device Utilization Summary for Altera Cyclone IV E

| Logic Utilization                      | Used |

|----------------------------------------|------|

| Number of Logic Elements combinational | 1803 |

| Number of Logic Elements registers     | 1496 |

| Number of Memory bits | 16384 |

|-----------------------|-------|

| Number of Pins        | 220   |

#### Table 9: Device Utilization Summary for Lattice ECP3

| Logic Utilization | Used |

|-------------------|------|

| Number of Slice   | 2503 |

| Number of PIO     | 220  |